Shifter Design using Multiplexers

1. Objectives

In this lab you will learn to develop shifters using multiplexers. First we will review some digital design concepts by creating an LPM module. Then, you will be designing a 1-bit 4-to-1 Multiplexer in Verilog, and use this module to build a shifter.

1.1 Reference Files for Lab

2. Prelabs

Before you come to lab, get familiar with shifters. You will find information on multiplexers in section 6.1 and shifters in section 7.8 of your text: “Fundamentals of Digital Logic with Verilog Design” by Brown and Vranesic.

3. Multiplexer and Shifter Design

Step 1: Using an LPM Module in QuartusII

Quartus II has a library of predefined functions and devices. This Library is called LPM, or Library of Parameterized Modules. Each module can be customized to perform in a specified manner. For the first step in the lab, you will use the LPM to create a 2-bit wide 2-to-1 Multiplexer.

For this step in the lab, you need to create a new project and a new .bdf file. Save this file as lab12astep1.bdf. Set the file to the top level entity, and right click anywhere inside the document. Select Insert | Symbol…. This will open an Enter Symbol Dialog Box. Click on the MegaWizard Plug In Manager, and in the next screen, select Create a new custom Megawizard variation and click next. In the next window, highlight LPM_MUX in the gates folder on the left-hand side. Select Verilog HDL, and choose a name for the module (e.g. mux2to1). Click next.

Now you will need to edit the ports and parameters. This is where you customize the selected modules. Leave the number of data inputs at 2, and change the width of the busses to 2. This forces the inputs, data0 and data1, and the output, result, to be 2-bit wide buses. Click next, finish, and finally ok. The design will then appear in the .bdf document.

Next, add 3 inputs an output to the LPM Design. Connect the inputs to the dataa , datab, and sel inputs on the LPM MUX. Connect the output to the result output on the LPM Mux. Rename the pin connected to dataa to i0[1..0], signifying there is a 2-bit wide bus. Rename the pins connected to datab, sel and result to i1[1..0], s, and f[1..0] respectively. When you are done, compile the project.

Create a waveform to simulate the design. Use the groups for i0, i1, and f (not i0[0], i0[1], etc.). Set the Radix to Hexadecimal (highlight node, right click and select properties). Notice that the displayed value of f[1..0] becomes X. This indicates the value is undetermined at this time.

Add enough test cases in the waveform to convince yourself that the Megawizard plus has worked as expected. When you are done, run the simulation. When you are satisfied, confirm your work with your TA.

Step 2: 4-1 Multiplexer in Verilog

We have designed a 4-1 Mux in verilog using a case

statement. We will now design one using

the conditional operator (?:).

The following is the verilog code for a 1-bit 2 to 1 multiplexer. When the selector is 0 the output f is i0 and when the selector is 1 the output is i1.

module mux2to1(i0, i1, s, f);

input i0, i1, s;

output f;

assign f = s ? i1 : i0;

endmodule

Modify this code to build a 1-bit 4-to-1 multiplexer. The multiplexer will have the following specification:

· Four 1-bit data inputs, W0, W1, W2 and W3.

· One 2-bit selector input, S [1..0].

· One 1-bit output, F.

· When the S [1..0] is 00 the output will be W0.

· When the S [1..0] is 01 the output will be W1.

· When the S [1..0] is 10 the output will be W2.

· When the S [1..0] is 11 the output will be W3.

As we saw in the above Verilog code, the following statement sets the f = i1 if s = 1 and f = i0 if s = 0.

assign f = s ? i1 : i0;

We want to build a 1-bit 4-to-1 multiplexer based upon this code. You’re code should have the same number of lines as before. HINT: The condition operator, ?:, will appear three times in your assign statement.

Once you are done with writing the Verilog code for the 1-bit 4-to-1 multiplexer, save it as mux4to1.v, compile it and create a symbol for it.

Step 3: Designing a Shifter in Schematics

You will now design a device called a Shifter. A Shifter is built from Multiplexers and shifts the outputs, based on the select signals. For this Shifter, you will use the 1-bit 4-to-1 multiplexer you made in Step 2.

Below is important imformation regarding the Shifter. The Shifter has the following inputs and outputs:

|

X3, X2, X1, X0 |

Primary Inputs |

|

X-1, X-2, X-3 |

Cascading Inputs |

|

S1, S0 |

Shift Count Inputs |

|

F3, F2, F1, F0 |

Fixed Outputs |

The Shifter assigns the F outputs from the inputs, shifted to the left 0, 1, 2,or 3 places as indicated by the 2-bit shift count (select signals). The table below summarizes the behavior:

|

S1 |

S0 |

F3 |

F2 |

F1 |

F0 |

|

0 |

0 |

X3 |

X2 |

X1 |

X0 |

|

0 |

1 |

X2 |

X1 |

X0 |

X-1 |

|

1 |

0 |

X1 |

X0 |

X-1 |

X-2 |

|

1 |

1 |

X0 |

X-1 |

X-2 |

X-3 |

Example:

Let the inputs have the values below:

|

X3 |

X2 |

X1 |

X0 |

X-1 |

X-2 |

X-3 |

|

a |

b |

c |

d |

e |

f |

g |

If the shift count is 00, we would have the output shown below:

|

F3 |

F2 |

F1 |

F0 |

|

|

|

|

a |

b |

c |

d |

e |

f |

G |

If we shifted left ONE position- shift count is 01:

|

|

F3 |

F2 |

F1 |

F0 |

|

|

|

a |

b |

c |

d |

e |

f |

G |

The Shift Count moves the window for the output!

To develop this Shifter, you need to start with a new project and a new .bdf. Name it shifter.bdf.

Hint:

To complete the Shifter design you will need four 1-bit 4-to-1 Muxes, one for each output of the shifter. As you can see from the above table which summarizes the behavior of a shifter, the output bit F3 of the shifter can be X3, X2, X1 or X0 depending on the value of the shift count. So you can use the 4-to-1 multiplexer to choose between them. X3, X2, X1 and X0 will form the inputs of the mux, while the shift count will be fed as the selector. In your class you learned how a basic shifter works and you also learnt how to build a 4-bit rotator using multiplexer. Your design for this lab will be similar (but not the same) to the rotator.

Once your circuit is ready compile it and assign the following pin locations.

Inputs:

|

INPUTS |

PIN LOCATIONS |

|

X3 |

16 |

|

X2 |

18 |

|

X1 |

20 |

|

X0 |

22 |

|

X-1 |

25 |

|

X-2 |

27 |

|

X-3 |

29 |

|

S0 |

8 |

|

S1 |

10 |

Outputs:

|

Outputs |

Pin Locations |

|

F3 |

60 |

|

F2 |

58 |

|

F1 |

56 |

|

F0 |

54 |

Remember that you need to assign the inputs pins to each

respective input. Connect one set of

dipswitches to the x inputs, and use the two push buttons for S0 and S1. Connect the output to the LEDs (see

below).

Once you have done the pin location assignment, compile again. Program the board.

Step 4: Testing

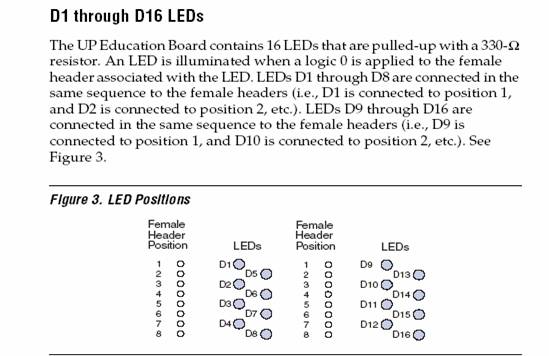

We shall use the LEDs on the board to test our design in this lab. The figure below gives you a description of how we can use the LEDs. Please read through the explanation.

So once you have programmed the board connect the output pins F3 through F0 to these LEDs using wires. Notice that a LED glows when logic 0 is applied, keep that in mind while you are interpreting your results. Give each input (X0 to X-3) a unique value. Make sure you step through each input combination for the shift count. When you are confident your design is correct, have your TA verify this.

Step 5: Completing Lab

This concludes the lab. Please save all files and logout.