# **MPC555 Interrupts**

by John Dunlop, Josef Fuchs, and Steve Mihalik Rev. 0, 26 July 2001

## 1 Introduction

The MPC555 has numerous timers, peripherals and input pins that can generate interrupts. This application note describes how the interrupts work and how to write software for their initialization and service routines.

Examples illustrate how interrupt handler routines written in assembler, C and even controlled by an operating system can have a dramatic variation in overhead. This overhead is almost entirely caused by the amount of context, (i.e., registers), saved and restored in the routine.

Although this application note focuses on interrupts, the discussion of context saving and restoring applies to other exceptions as well as other Motorola PowerPC<sup>™</sup> microcontrollers. In addition, later MPC5xx microprocessors include an enhanced interrupt controller which has features to reduce latency. A summary of these features, which are optional to use in these later microcontrollers is listed in **Section Appendix B Enhanced Interrupt Controller Summary**.

## 2 Background

#### 2.1 Interrupts versus Exceptions

Definitions of "interrupts" and "exceptions" are not always consistent in PowerPC<sup>™</sup> literature. The following definitions are used for this application note.

**Exceptions** are events that change normal program flow and machine state. Some examples of exceptions are reset, decrementer passing zero, system call instruction, various bus access errors, and even a software or hardware debugger. When an exception occurs, a short hardware context switch takes place and the processor branches to an address (exception vector) which is unique for each type of exception.

**Interrupts** are one type of exception. They are caused by interrupt requests from input pins or devices, such as internal peripherals. As specified in the PowerPC<sup>™</sup> architecture, all interrupts are required to share one exception vector offset, called "external interrupts", normally at 0x500. The term "external interrupts" include all interrupts external to the CPU core, not just external to the chip. The terms "external interrupts" and "interrupts" are the same in this application note.

### 2.2 Interrupt Sources and Levels

An interrupt source is a device that can initiate an interrupt. For the MPC555, these are:

- Input pins IRQ[0:7]

- Internal timers: time base (TBL), programmable interrupt timer (PIT), or real-time clock (RTC)

- PLL change of lock detector

© Freescale Semiconductor, Inc., 2004. All rights reserved.

© MOTOROLA INC., 2001

• Peripheral modules on the intermodule bus (IMB3): TPU3, QADC, QSMCM, MIOS, and TouCAN.

An **interrupt level** is a number which is assigned by software to all interrupt sources **except** input pins IRQ[0:7]. This number, or level, provides a mapping mechanism for software to identify which interrupt source is causing an interrupt request. Levels also imply a priority if two or more interrupt requests occur at the same time (see **Table 8** for priorities of input pins and levels). Interrupt pins do not get assigned levels because they have fixed priorities.

#### 2.3 Exception Vector and Exception Vector Table

An **exception vector** is an address where the processor begins execution after an exception is recognized and the immediate state of the machine saved. (This differs from 68000 architecture where vectors are pointers — PowerPC vectors have fixed locations.) Each exception has its own exception vector, which is the sum of a base address and a vector offset:

+ Exception Base Address + Exception Vector Offset ------Exception Vector

The **exception base address** is commonly either 0x0 or 0xFFF0 0000, depending on if the MSR[IP] bit. The base can have alternate values with exception vector "relocation" discussed later.

Each exception has its own exception vector offset. The normal offsets are shown in Table 1.

| Name of Exception                      | Offset |

|----------------------------------------|--------|

| System Reset or Non-Maskable Interrupt | 0x100  |

| Machine Check                          | 0x200  |

| Reserved                               | 0x300  |

| Reserved                               | 0x400  |

| External Interrupts                    | 0x500  |

| etc.                                   | etc.   |

#### **Table 1 Normal Exception Vector Offsets**

An **Exception Vector Table**, sometimes just called exception table, is a table of exceptions and their vectors. For example, if the exception base address = 0x0, then the table is simply the exception vector offsets (as in the prior paragraph). If the exception base address is 0xFFF0 0000, then the exception vector table is shown in Table 2.

| Table 2 Exam | ple Exception | Vector Table |

|--------------|---------------|--------------|

|--------------|---------------|--------------|

| Name of Exception                      | Exception Vector |

|----------------------------------------|------------------|

| System Reset or Non-Maskable Interrupt | 0xFFF0 0100      |

| Machine Check                          | 0xFFF0 0200      |

| Reserved                               | 0xFFF0 0300      |

| Reserved                               | 0xFFF0 0400      |

| External Interrupts                    | 0xFFF0 0500      |

| etc.                                   | etc.             |

#### 2.4 Exception Table Relocation

A feature in the MPC555 allows having tighter exception vector offsets for the purpose of saving memory space. This feature, called **exception table relocation**, "relocates" exception vector offsets by:

- "Relocating" exception vector offsets to be eight bytes apart, instead of 0x100 (256) bytes.

- Allowing additional exception vector base values of: 0x8000 (32 Kbytes)<sup>1</sup> and/or bases which move with the mapping of the internal memory space base, as indicated in the internal memory mapping register, IMMR[ISB] bit field.

To use the relocation feature, the control bits in Table 3 are used.

| Register[Bit]             | Bit Name                          | Description                                                                                                                              |

|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| MSR[IP]                   | Instruction Prefix                | Controls the main base address, either at 0x0 or 0xFFF0 0000.                                                                            |

| BBCMCR[ETRE]              | Exception Table Relocation Enable | Enables exception vector addresses<br>relocation. Addresses are separated by 8<br>bytes instead of 256 bytes. (Requires<br>MSR[IP] = 1.) |

| BBCMCR[OERC] <sup>1</sup> | Other Exception Relocation Enable | Provides an additional offset to the base address when relocation is used.                                                               |

| IMMR[ISB]                 | Internal Memory Space Base        | Moves exception table base with internal memory space. (Requires MSR[IP] = 1 and BBCMCR[ETRE] = 1.)                                      |

#### **Table 3 Relocation Feature Control Bits**

NOTES:

1. On the MPC565 and other future members of the MPC5xx family the OERC field is two bits wide instead of one and is located in different bit positions of the BBCMCR. Two bits allows for more possible exception locations. See the information below (assumes MSR[IP] = 1 and BBCMCR[ETRE] = 1).

| INIP COOO   | INIPC 303 |       |                          |

|-------------|-----------|-------|--------------------------|

| <u>OERC</u> | OERC0     | OERC1 | Exception Table Location |

| 0           | 0         | 0     | 0x0 + ISB offset         |

| 1           | _         | _     | 0x8 000 + ISB offset     |

| _           | 0         | 1     | 0x1 0000 + ISB offset    |

| _           | 1         | 0     | 0x8 0000 + ISB offset    |

| _           | 1         | 1     | 0x3F E000 + ISB offset   |

|             |           |       |                          |

#### CAUTION

When using the relocation feature, a branch absolute (ba) instruction, not just a branch (b) instruction, must be used at each relocated vector address. Otherwise exceptions will not work.

A complete table of all possible exception vectors is listed in **Table 4** when the internal memory space base (ISB) is at 0x0.

<sup>1.</sup> On future MPC5xx parts with larger flash blocks, this address will be 0x1 0000 (the second 64 Kbyte flash block). In addition, these parts can map the exception table to the internal RAM and to the second flash module (if present).

| Name of Exception                   | Exception Vector<br>MSR[IP] = 0 | Exception Vector<br>MSR[IP] = 1<br>ETRE = 0 | Exception Vector<br>MSR[IP] = 1<br>ETRE = 1<br>OERC = 0<br>ISB = 000 | Exception Vector<br>MSR[IP] = 1<br>ETRE = 1<br>OERC = 1<br>ISB = 000 |

|-------------------------------------|---------------------------------|---------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| Reserved                            | 0x0000 0000                     | 0xFFF0 0000                                 | 0x0000 0000                                                          | 0x0000 8000                                                          |

| System Reset, NMI Interrupt         | 0x0000 0100                     | 0xFFF0 0100                                 | 0x0000 0008                                                          | 0x0000 0008 <sup>1</sup>                                             |

| Machine Check                       | 0x0000 0200                     | 0xFFF0 0200                                 | 0x0000 0010                                                          | 0x0000 8010                                                          |

| Reserved                            | 0x0000 0300                     | 0xFFF0 0300                                 | 0x0000 0018                                                          | 0x0000 8018                                                          |

| Reserved                            | 0x0000 0400                     | 0xFFF0 0400                                 | 0x0000 0020                                                          | 0x0000 8020                                                          |

| External Interrupt                  | 0x0000 0500                     | 0xFFF0 0500                                 | 0x0000 0028                                                          | 0x0000 8028                                                          |

| Alignment                           | 0x0000 0600                     | 0xFFF0 0600                                 | 0x0000 0030                                                          | 0x0000 8030                                                          |

| Program                             | 0x0000 0700                     | 0xFFF0 0700                                 | 0x0000 0038                                                          | 0x0000 8038                                                          |

| Floating-Point Unavailable          | 0x0000 0800                     | 0xFFF0 0800                                 | 0x0000 0040                                                          | 0x0000 8040                                                          |

| Decrementer                         | 0x0000 0900                     | 0xFFF0 0900                                 | 0x0000 0048                                                          | 0x0000 8048                                                          |

| Reserved                            | 0x0000 0A00                     | 0xFFF0 0A00                                 | 0x0000 0050                                                          | 0x0000 8050                                                          |

| Reserved                            | 0x0000 0B00                     | 0xFFF0 0B00                                 | 0x0000 0058                                                          | 0x0000 8058                                                          |

| System Call                         | 0x0000 0C00                     | 0xFFF0 0C00                                 | 0x0000 0060                                                          | 0x0000 8060                                                          |

| Trace                               | 0x0000 0D00                     | 0xFFF0 0D00                                 | 0x0000 0068                                                          | 0x0000 8068                                                          |

| Floating-Point Assist               | 0x0000 0E00                     | 0xFFF0 0E00                                 | 0x0000 0070                                                          | 0x0000 8070                                                          |

| Reserved                            | 0x0000 0F00                     | 0xFFF0 0F00                                 | 0x0000 0078                                                          | 0x0000 8078                                                          |

| Software Emulation                  | 0x0000 1000                     | 0xFFF0 1000                                 | 0x0000 0080                                                          | 0x0000 8080                                                          |

| Reserved                            | 0x0000 1100                     | 0xFFF0 1100                                 | 0x0000 0088                                                          | 0x0000 8088                                                          |

| Reserved                            | 0x0000 1200                     | 0xFFF0 1200                                 | 0x0000 0090                                                          | 0x0000 8090                                                          |

| Instruction Protection Error        | 0x0000 1300                     | 0xFFF0 1300                                 | 0x0000 0098                                                          | 0x0000 8098                                                          |

| Data Protection Error               | 0x0000 1400                     | 0xFFF0 1400                                 | 0x0000 00A0                                                          | 0x0000 80A0                                                          |

| Reserved                            | 0x0000 1500-<br>0x0000 1BFF     | 0xFFF0 1500-<br>0xFFF0 1BFF                 | 0x0000 00A8-<br>0x0000 00DF                                          | 0x0000 80A8-<br>0x0000 80DF                                          |

| Data Breakpoint                     | 0x0000 1C00                     | 0xFFF0 1C00                                 | 0x0000 00E0                                                          | 0x0000 80E0                                                          |

| Instruction Breakpoint              | 0x0000 1D00                     | 0xFFF0 1D00                                 | 0x0000 00E8                                                          | 0x0000 80E8                                                          |

| Maskable External Breakpoint        | 0x0000 1E00                     | 0xFFF0 1E00                                 | 0x0000 00F0                                                          | 0x0000 80F0                                                          |

| Non-Maskable External<br>Breakpoint | 0x0000 1F00                     | 0xFFF0 1F00                                 | 0x0000 00F8                                                          | 0x0000 80F8                                                          |

**Table 4 Exception Vector Table Alternatives**

NOTES:

System reset/NMI uses 0x0000 0008 instead of 0x0000 8008 in the MPC555 because system reset clears the OERC bit, although NMI does not. However, later MPC5xx processors such as the MPC565/MPC566 behave differently — OERC can be set in the Reset Configuration Word or in the BBCMCR.

#### 2.5 Non-Interrupt Exceptions

Although this application note focuses on the setup, control and use of interrupts, it is worthwhile to briefly describe a number of other common 'useful' exceptions available on the PowerPC core.

#### 2.5.1 System Reset: Vector Offset = 0x100

The reset exception is taken from a number of sources as listed below. For more information, see SEC-TION 7, RESET, in the *MPC555 User's Manual* (MPC555UM/AD).

- Reset pins PORESET, HRESET, or SRESET

- IRQ[0], which is a non-maskable interrupt pin

- Clock: loss of lock or on-chip clock switch

- Software watchdog timer (if SYPCR[SWRI] is clear)

- Checkstop condition

- Debug or JTAG port

Depending on the source of reset, three levels of accompanying hardware initializations occur: poweron, hard or soft. Thus, it must be remembered that from executing from vector 0x100 the controller can be in different states, appropriate care must be used. To check the source of reset, and thus the implications to the MPC555, it is possible to check the RSR register. The RSR bits can only be cleared by power-on and software writing a "1" to them.

#### 2.5.2 NMI interrupt: Vector Offset = 0x100

A non-maskable interrupt (NMI) is generated from one of two sources:

- The software watchdog timer (if the SYPCR[SWRI] bit is set)

- The IRQ[0] pin

Semiconductor, Inc

eescale

When an NMI exception occurs, the reset vector offset is used. Consequently it may be necessary to check if it was a NMI that occurred because, *unlike the reset, many of the initialization events to registers do not occur*. The NMI is taken asynchronously to the program flow, can never be masked and has the highest priority.

Because NMI is not maskable, there is risk that an NMI exception may not be recoverable. Therefore it should not be used for normal applications but used only for emergency.

#### NOTE

The IRQ[0] can generate an interrupt to the core as well, this operation is undesired. IRQ[0] should always be masked in the SIPEND register.

#### 2.5.3 Machine Check: Vector Offset = 0x200

This separate exception informs of any memory access violations such as non-existent addresses, data errors or a violation of the memory protection type. The exception can occur for both internal and external memory areas. For a machine check exception to occur, it must be enabled by setting the MSR[ME] bit before the memory violation takes place. Otherwise (if MSR[ME]=0) no machine check exception is generated, but the checkstop state is entered. The behavior of the checkstop state is determined by the PLPRCR[CSR] bit.

#### 2.5.4 Floating-Point Unavailable: Vector Offset = 0x800

As the name suggests, the vector occurs when floating-point instructions are being used without the floating point unit being enabled. A common cause of this is when software attempts floating-point instructions during an exception routine, but the floating-point unit was disabled at the beginning of the exception routine. Therefore, it can be used to trap and re-enable the floating-point unit when not done so in another exception service routine.

#### 2.5.5 Decrementer: Vector Offset = 0x900

The decrementer and closely associated time base counters are defined within the PowerPC architec-

ture as 32-bit decrementing and 64-bit incrementing counters. Both counters are only accessible as special-purpose register accesses and thus cannot be accessed as memory mapped modules. The major difference between them is that the time base counter causes an interrupt on offset 0x500 while the decrementer provides a separate exception at 0x900.

The decrementer will cause an exception when it rolls over from all zeros to the LSB being set high again to begin the counting process. The count value is configurable through the DEC register (SPR22) but must be set through the use of the special MFSPR and MTSPR (move from and move to special purpose register) PowerPC instructions. On the MPC555, the decrementer clock is a subdivision of the processor clock. The clock source is either the system clock (divided by 16) or the oscillator clock input (divided by 4 or 16) as specified in the time base source bit (TBS) in the system clock control register (SCCR). The decrementer is enabled by the TBE bit in the time base status and control register (TB-SCR).

Although, there are other counters on the MPC555, the decrementer has the advantage of requiring no decoding for the exception vector and thus is useful for frequently called timer periods, such as an operating system ticks.

#### 2.5.6 Floating-Point Assist: Vector Offset = 0xE00

The purpose of this exception is to provide a mechanism to call a software envelope (routines) to fully implement the IEEE-754 floating-point specification. The software routine handles a number of extreme conditions that are rare and expensive to implement in hardware. The software routine will impact the size and the effect on the average instruction processing speed.

Non-IEEE mode is typically recommended for embedded applications because of faster execution. However, non-IEEE mode can not cause this execption. See *RCPURM/AD* Section 3.4.3 for further information.

#### 2.5.7 Data and Instruction Breakpoints Exception: Vector Offsets = 0x1C00 and 0x1D00

In most cases, these exception vectors are not used. They are reserved for a non-BDM debugger (software monitor) or some user-specific exception. Noirmally the BDM is entered as a result of a data and instruction breakpoint, then the MPC555 executes instructions received serially via the BDM link. For more information, see **SECTION 21**, **DEVELOPMENT SUPPORT**, in the **MPC555 User's Manual** (MPC555UM/AD).

#### 2.5.8 Maskable and Non-Maskable External Breakpoints Exceptions: Vector Offsets = 0x1E00 and 0x1F00

As stated in Section 2.5.7 Data and Instruction Breakpoints Exception: Vector Offsets = 0x1C00 and 0x1D00, these exception vectors are not used in most systems. They are reserved for a non-BDM debugger (software monitor) or some user-specific exception. Typically the BDM is entered as a result of a maskable and non-maskable external breakpoint, then the MPC555 executes instructions received serially via the BDM link. For more information, see SECTION 21, DEVELOPMENT SUPPORT, in the MPC555 User's Manual (MPC555UM/AD).

#### 2.6 Recoverable Exception [Interrupt]

Sometimes when an exception occurs it may not be possible to recover the machine state. The recoverable interrupt bit in the machine state register, MSR[RI], is a status bit indicating this condition

If a non-maskable exception occurs such as reset, breakpoints or a machine check, software can poll the MSR[RI] bit to determine if the machine can recover its state. This bit changes state either automatically by hardware or manually under software control. Section 7 Examples of Initialization and In-

terrupt Service Routines will discuss how and when exception routine software must set or reset it.

#### 2.7 EABI Standard

Embedded application binary interface (EABI) is a set of software conventions. They span areas such as register usage, stack layout and parameter passing. Examples of EABI conventions are dedicating register r1 the stack pointer, organizing the stack in frames, and assigning certain general-purpose registers (gprs) and floating point registers (fprs) as volatile and nonvolatile among function calls. Compiler and debug tool vendors have adopted EABI conventions for interoperability. Refer to the *Embedded Application Environments Interface*, EABI/D.

## 3 MPC555 Interrupt System

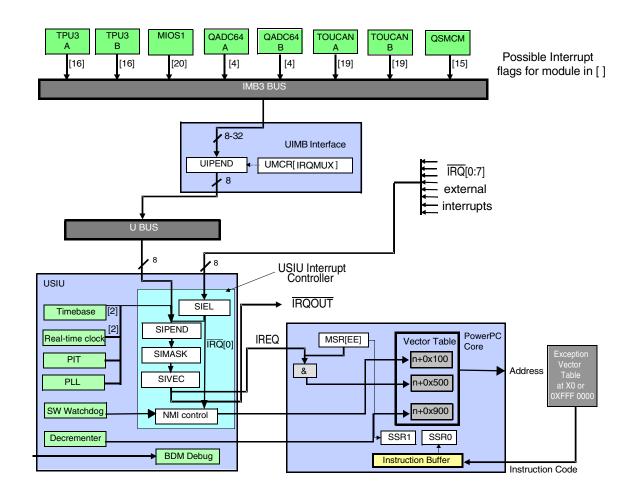

**Figure 1** contains a block diagram of the overall interrupt system. This system will be discussed by starting with the MPC555 core and working out to the peripheral devices.

NOTE

This application note will assume the exception relocation feature is not used.

Figure 1 Overall MPC555 Interrupt System

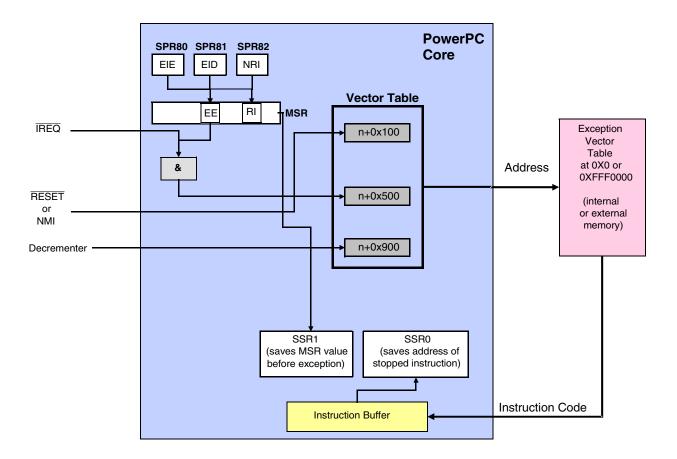

#### 3.1 PowerPC Core Interrupt

The PowerPC core has only a single interrupt input, which is from the interrupt controller. See **Figure 2**. This interrupt is enabled by the external interrupt enable (EE) bit in the machine state register (MSR). Besides enabling interrupt exceptions, this bit also enables the decrementer exception.

**NOTE**: The MSR[EE] bit must be set in order to allow the PowerPC processor to recognize any interrupts.

Figure 2 PowerPC Core Interrupt

(without Vector Table Relocation)

Before recognizing the interrupt exception, all instructions being executed are completed. Once the core recognizes any exception, hardware automatically performs a machine state saving context switch as shown in **Table 5**.

#### NOTE

Only negate interrupt sources while MSR[EE] = 0. Software should disable interrupts in the CPU core (by clearing this bit) prior to masking or disabling any interrupt which might be currently pending at the CPU core.

After disabling an interrupt, sufficient time should be allowed for the negated signal to propagate to the CPU core, prior to re-enabling interrupts. The worst case time is an interrupt from an IMB3 module, which would be six clocks if the IMB3 is in full speed mode (UMCR[HSPEED] = 0) or 12 clocks if the IMB3 is in half-speed mode (UMCR[HSPEED] = 1).

| Register/Pointer       | Action                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRR0                   | Gets loaded with an instruction address depending on the exception. For interrupts and most other exceptions, it is address of the next instruction, (i.e., the instruction that would have been executed if the interrupt exception did not occur).<br>(Previous SRR0 contents are overwritten.)                                                                                            |

| SRR1                   | SRR1[0:15] gets loaded with information depending on exception type.<br>SRR1[16:31] gets loaded with MSR[16:31].<br>(Previous SRR1 contents are overwritten.)                                                                                                                                                                                                                                |

| MSR                    | Recoverable exception status bit is cleared (RI=0)<br>Privilege level is set to supervisor and user (PR=0)<br>Little-endian mode is disabled (LE=0)<br>Maskable exceptions are disabled, which are:<br>– External interrupt exceptions (EE=0)<br>– Floating-point unit <b>and</b> floating point exceptions (FP=FE0=FE1=0)<br>– Single-step trace exceptions (SE=0)<br>– Branch trace (BE=0) |

| Instruction<br>Pointer | Branches to start execution at the interrupt exception "vector". By default, this is location $0x500$ (assuming the MSR.IP bit = 0 and exception relocation is not enabled).                                                                                                                                                                                                                 |

Table 5 Exception Context Switch Automatically Done By Hardware

As mentioned in Section 2.6 Recoverable Exception [Interrupt], the purpose of the MSR[RI] bit is to indicate non-recoverable situations. For example: an interrupt exception occurs, causing hardware to back up the next instruction and MSR bits to SRR0:1. If SRR0:1 are not backed up somewhere and another exception occurs, their contents are lost. Hence the original state and instruction address prior to the interrupt is lost. As will be shown later, interrupt exception software typically will need to back up SRR0:1 and then set MSR[RI] = 1 to indicate the state is recoverable.

The EIE, EID, and NRI special purpose registers have the sole purpose of providing a mechanism to quickly modify the MSR[RI] and MSR[EE] bits. Any writes to these registers cause these bits to be set or cleared as in the table below. Writing to these registers can only be done in assembler because they are special purpose registers, not memory-mapped. Hence they are not accessible from the c language. To access them we must use the assembly language instruction "mtspr". For example see below and **Table 6**.

mtspr EID, r0 ; Set RI bit = 1 and EE bit = 0 in MSR

| SPR | Mnemonic | MSR[EE] | MSR[RI] |

|-----|----------|---------|---------|

| 80  | EIE      | 1       | 1       |

| 81  | EID      | 0       | 1       |

| 82  | NRI      | 0       | 0       |

#### Table 6 Manipulating EE and RI Bits

At the end of the interrupt routine, executing a return from interrupt (rfi) instruction restores the context by hardware. This causes the action shown in **Table 7**.

#### **Table 7 Return From Interrupt Context Switch**

| Register/Pointer       | Action                                                                                                                             |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| MSR                    | MSR[16:31] gets re-loaded from SRR1 (enabling external interrupts, other maskable exceptions, etc. again.)                         |

| Instruction<br>Pointer | Gets re-loaded from SRR0, which resumes program execution after the last executed instruction before the interrupt was recognized. |

#### 3.2 USIU Interrupt Controller

The main interrupt controller is in the USIU module. However, there are interrupt controller functions in other areas, such as the level mapping of peripherals in the UIMB module (see Section 3.6 Interrupt Sources: UIMB Peripherals).

The USIU interrupt controller has 16 inputs: eight external interrupt request pins (IRQ[0:7]) and eight internal interrupt "levels". As mentioned in **Section 2.2 Interrupt Sources and Levels**, levels are a mapping mechanism for interrupt sources and imply a priority. Interrupt sources inside the USIU (time base, real-time clock, PIT and PLL change of lock detector) are assigned a level 0:7. Interrupt sources from peripherals on the IMB3 bus can have levels 0:31. However, these IMB3 bus peripherals with levels 7:31 are all mapped to level 7 of the USIU interrupt controller (see **Section 3.4 Interrupt Sources**).

The 16 USIU interrupt controller inputs (8 pins and 8 levels) are fed into the **SIPEND** (USIU interrupt pending register). Software can read this register to see which of the 16 interrupts are pending.

#### NOTE

The MPC565 and other future MPC5xx family members have an enhanced interrupt controller that is backwards compatible to the MPC555. The new features must explicitly be enabled.

Figure 3 USIU Interrupt Structure

The **SIMASK** (USIU mask register) contains corresponding mask bits for each SIPEND interrupt bit. In order for interrupts to be fed into the CPU core, the corresponding mask bit must be set. At RESET, the SIMASK register is set to all 0's, disabling all interrupt sources.

SIMASK[IRM0] bit is a special case. This is the mask bit for the IRQ[0] input pin, which is a non-maskable interrupt. Setting this bit to 0 has no effect.

After the SIPEND and SIMASK registers, there is a priority arbiter and encoder. This gives a number called interrupt code to the highest priority unmasked interrupt. If two or more unmasked interrupt requests occur at the same time, the one with the lowest numbered interrupt code will have priority.

The interrupt code is located in a field of the **SIVEC** (USIU interrupt vector register). during the interrupt service routine, the interrupt code will be used as in index into a branch table for branching to the appropriate interrupt source's service routine. This is why each interrupt code is separated by four bytes, the width of one instruction. See **Table 8**.

#### NOTE

Other lower priority or masked interrupt requests can be examined at any time by reading the SIPEND register. If no unmasked interrupt request is pending, the Interrupt Code has a default value of 0x3C.

| Priority    | Interrupt Source              | Interrupt Code<br>(Binary) | Interrupt Code<br>(Hex) |

|-------------|-------------------------------|----------------------------|-------------------------|

| 0 (highest) | IRQ[0] Input Pin <sup>1</sup> | 00000000                   | 0x0                     |

| 1           | Level 0                       | 00000100                   | 0x4                     |

| 2           | IRQ[1] Input Pin              | 00001000                   | 0x8                     |

| 3           | Level 1                       | 00001100                   | 0xC                     |

| 4           | IRQ[2] Input Pin              | 00010000                   | 0x10                    |

| 5           | Level 2                       | 00010100                   | 0x14                    |

| 6           | IRQ[3] Input Pin              | 00011000                   | 0x18                    |

| 7           | Level 3                       | 00011100                   | 0x1C                    |

| 8           | IRQ[4] Input Pin              | 00100000                   | 0x20                    |

| 9           | Level 4                       | 00100100                   | 0x24                    |

| 10          | IRQ[5] Input Pin              | 00101000                   | 0x28                    |

| 11          | Level 5                       | 00101100                   | 0x2C                    |

| 12          | IRQ[6] Input Pin              | 00110000                   | 0x30                    |

| 13          | Level 6                       | 00110100                   | 0x34                    |

| 14          | IRQ[7] Input Pin              | 00111000                   | 0x38                    |

| 15          | Level 7                       | 00111100                   | 0x3C<br>(Default value) |

| 16-31       | Reserved                      | —                          | —                       |

#### **Table 8 Interrupt Priority and Codes**

NOTES:

1. IRQ[0] Input Pin is a special case. See 3.3 Interrupt Sources: External IRQ Pins.

#### 3.3 Interrupt Sources: External IRQ Pins

As shown in the interrupt code table previously, the eight interrupt pins have unique interrupt codes. The system designer must ensure the application's higher priority external interrupts have lower number interrupts. Each external interrupt pin has a mask bit in the SIMASK register to enable it.  $\overline{IRQ}[0:7]$  have six priorities and interrupt code. The hardware design must connect higher priority interrup signals to the lower number of interrupt pins, such as  $\overline{IRQ}[1]$  or  $\overline{IRQ}[2]$ .

**IRQ**[0] is a special case. This is non-maskable and causes a NMI exception. It uses the reset exception vector offset, **but does not cause an actual reset**. Hence the exception vector will be 0x100 instead of 0x500. If the RESET exception routine needs to determine the cause of the reset, then the reset status register (RSR) and SIPEND[IRQ0] bit are examined.

#### CAUTION

Because IRQ[0] can cause a nonmaskable exception, it can cause an irrecoverable condition. Therefore, it should not be used for a normal application input.

#### NOTE

A software watchdog can also cause a NMI reset. IRQ[0] is ALWAYS edge triggered.

The **SIEL** (USIU interrupt edge level register) contains bits for IRQ[0:7] input pins to specify if the interrupt is caused by a falling edge (ED=1) or simply a low level (ED=0).

Typically a falling edge interrupt input (ED=1) is used. In this case, the appropriate bit in the SIPEND must be cleared in the interrupt service routine when a falling edge interrupt occurs.

Low level interrupt inputs (ED=0) are used for wired-OR situation of multiple sources on one line. When an interrupt of this type occurs, the interrupt service routine must ensure the interrupt line is returned to the inactive high state before exiting the interrupt service routine.

#### 3.4 Interrupt Sources: USIU Internal Devices

All interrupt sources except external IRQ pins must be given level assignments in some register (see **Section Appendix A Table of Potential Interrupt Sources**). These level assignments map the interrupt source to an input of the USIU interrupt controller. When the interrupt source attempts to initiate an interrupt request, its level to the USIU interrupt controller becomes active. The interrupt controller will recognize the interrupt if:

- Interrupts are enabled in the MSR[EE] bit

- The level is not blocked in the SIMASK register

- The level is not competing with a higher priority interrupt request.

Levels in the USIU interrupt sources are assigned in an 8-bit field with the format in **Table 9**. A common mistake made is to attempt to use a binary value of the level instead of the pattern shown in **Table 9**.

| Level Assignment | Binary Value | Hex Value |

|------------------|--------------|-----------|

| 0                | 1000000      | 0x80      |

| 1                | 0100000      | 0x40      |

| 2                | 00100000     | 0x20      |

| —                | —            | —         |

| 7                | 0000001      | 0x01      |

#### **Table 9 IUSIU Interrupt Level Assignments**

The USIU has four interrupt sources:

- 1. Programmable interrupt timer (PIT)

- 2. Time base (TB)

- 3. Real-time clock (RTC)

- 4. Phase lock loop change of lock (PLL)

Some sources can cause an interrupt from more than one condition, but each has only one interrupt level. For example, the time base has one level but can cause an interrupt when it matches either one of two time base reference registers TBREFA or TBREFB. Each time base reference has its own interrupt enable bit and each has its own status bit. If both are enabled, the time base interrupt service routine must check the status bits to determine which caused the interrupt.

For More Information On This Product, Go to: www.freescale.com

#### NOTE

Some interrupt sources have a freeze control bit. Generally this allows timers to keep incrementing or decrementing if the FREEZE debug signal is asserted. The FREEZE signal allows users to stop various clocks to aid debugging. It is active when in debug mode, (i.e., when instructions are executed from the debug port) instead of from memory.

#### EXAMPLE

*PIT Interrupt.* The steps below will generate an interrupt request at the interrupt controller when the PIT crosses zero. We will not enable interrupts to the core in this example. If you have an evaluation board with visibility into registers and bit fields, this would be a simple exercise to start understanding and experimenting with interrupts. It assumes the default clock to the PIT is used and is enabled.

- 1. Set PITC[PITC]=0x1000 for a modulus count (gets loaded when PITR decrements passed 0)

- 2. Make sure PISCR[PITF]=0 to keep PIT the clock running during while the debug signal FREEZE is asserted. (0 is the default value from reset.)

- 3. Set PISCR[PIRQ] = 0x40 to set the PIT's interrupt level to level 0

- 4. Enable level 0 by setting SIMASK[LVLM0]=1

- 5. Set PISCR[PTE]=1 to enable the PIT clock to decrement.

- 6. Enable PIT interrupt by setting PISCR[PIE] = 1

Now watch the PIT decrement. When it reaches 0, the PIT status bit PISCR[PS] will set, which sets the SIPEND bit for level 0 and the interrupt code in SIVEC to level 0. The PISCR[PS] will stay set until a "1" is written to that bit, which means SIPEND will stay active for level 0 until, (e.g., a "1" is written to that bit). The processor does not take the interrupt exception because the MSR[EE] bit has not been set.

#### 3.5 UIMB Module

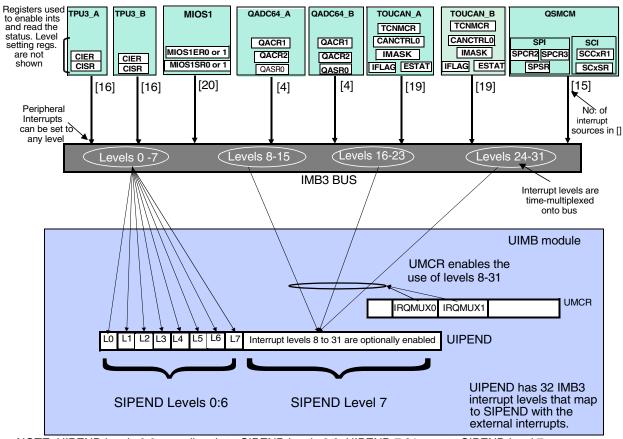

All interrupts from peripherals on the IMB are passed into the UIMB module. The UIMB module has an interrupt controller function of reducing up to 32 possible interrupt levels to 8 levels. These 8 levels go to the SIPEND register in the USIU Interrupt Controller. To achieve this reduction, IMB peripheral interrupt levels 7:31 all get mapped to level 7 as shown in Figure 4.

NOTE: UIPEND levels 0:6 map directly to SIPEND levels 0:6. UIPEND 7:31 map to SIPEND level 7.

#### Figure 4 Peripherals and the UIMB Interrupt Structure

Table 10 summarizes the mapping.

| Interrupt Level<br>from IMB Peripheral to<br>UIMB Module | Interrupt Level from<br>UIMB Module to USIU<br>Interrupt Controller | Relative Overhead to Identify<br>Interrupt Source |

|----------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------|

| 0                                                        | 0                                                                   | Fast – use SIVEC only                             |

| 1                                                        | 1                                                                   | Fast – use SIVEC only                             |

| 2                                                        | 2                                                                   | Fast – use SIVEC only                             |

| 3                                                        | 3                                                                   | Fast – use SIVEC only                             |

| 4                                                        | 4                                                                   | Fast – use SIVEC only                             |

| 5                                                        | 5                                                                   | Fast – use SIVEC only                             |

| 6                                                        | 6                                                                   | Fast – use SIVEC only                             |

| 7:31                                                     | 7                                                                   | Normal – use SIVEC and UIPEND                     |

IMB peripherals needing faster interrupt response should use levels 0 through 6 since only SIVEC register is necessary to identify the interrupt source, unless more than one source shares the same level. IMB interrupt levels 7:31 are all "shared" on level 7 input to the USIU interrupt controller. Hence additional decoding of a source is normally required, which would use the UIPEND register.

The **UIPEND** register reflects the status of the 32 IMB interrupt levels. It is a read-only register.

The levels coming into the UIMB from the UIMB peripherals use multiplexing for efficiency. Levels in these peripherals are represented by five bits [0:31]. The UIMB does not read all levels at once. It time multiplexes a three-bit level value [0:7] with four time slots as shown in **Table 11**.

| Multiplexed 3-bit<br>Level | 2-bit Time Slot | Generated IRQ Level |

|----------------------------|-----------------|---------------------|

| 0 7                        | 0               | 0 7                 |

| 0 7                        | 1               | 8 15                |

| 0 7                        | 2               | 16 23               |

| 0 7                        | 3               | 24 31               |

Table 11 UIMB Time Multiplexing

The **UMCR** register contains the control bits called IRQMUX to enable mapping of 32 possible interrupt requests from the UIPEND to the eight interrupt inputs of the USIU interrupt controller.

#### 3.6 Interrupt Sources: UIMB Peripherals

The UIMB interrupt sources include the following peripheral modules on the UIMB bus: two TouCAN modules, two QADC modules, two TPU modules, one MIOS1 module, and one QSMCM module. Each module has numerous conditions that can cause an interrupt, but have only one or two interrupt levels.

For example, any of a TPU's 16 channels can be set up to cause an interrupt, but there is only one interrupt line (level) leaving the module. (See **Table 25**.) The interrupt service routine must determine not only that the TPU caused the interrupt, but which channel caused it as well.

Levels are assigned in the module's level register. Although there are 32 possible levels, they are multiplexed on to eight inputs to the UIMB. For historical reasons, peripherals designate levels in two possible methods:

1. A single 5 bit "level" field, for levels 0 – 31 as follows. This applies to interrupt sources in USIU, QADC, and QSMCM modules.

| 5-bit Level Field Value | Level |

|-------------------------|-------|

| 00000                   | 0     |

| 00001                   | 1     |

| 00010                   | 2     |

| _                       | _     |

| 11111                   | 31    |

Table 12 UIMB Interrupt Level Assigment for 5-bit Level Field

2. A 3-bit "level" field for levels 0:7 and a 2 bit "time multiplex" or "byte select" field for multiplexing levels to a time slot. This applies to interrupt sources in TPU3 and MIOS1 modules.

| 3-bit Level Field Value | 2-bit Time Multiplex or<br>Byte Select Field | Peripheral Interrupt<br>Level |

|-------------------------|----------------------------------------------|-------------------------------|

| 000 to 111              | 00                                           | 0 to 7                        |

| 000 to 111              | 01                                           | 8 to 15                       |

| 000 to 111              | 10                                           | 16 to 23                      |

| 000 to 111              | 11                                           | 24 to 31                      |

Table 13 UMB Interrupt Level Assignment for 3- and 2-bit Level Flelds

A common rule is to have each module use a different interrupt level to minimize interrupt service routine time in determining the source of the interrupt. The lower number levels have priority of higher numbers if two interrupts occur at the same time, so the more important interrupt sources must reside at lower levels.

As shown in the tables of **Section Appendix A Table of Potential Interrupt Sources**, UIMB modules have multiple interrupt sources sharing a level. The enable bits must be set for the desired interrupt sources. When an interrupt condition is met, such as a communication buffer becoming empty, that condition is "anded" with its enable bit to determine if an interrupt request gets passed on. The interrupt service routine, once identifying the module causing an interrupt, checks the status bits for determining the specific interrupt source causing the interrupt.

#### 3.7 A Note on Interrupt Nesting

Once an interrupt has been recognized by the core, the hardware context switch disables further interrupts. There are two options:

- 1. No interrupt nesting: Keep interrupts disabled during the entire interrupt service routine.

- 2. Interrupt nesting: Enable interrupts in a window inside the interrupt service routine.

If the interrupt service routine is relatively short, no nesting is necessary. If nesting is used, additional steps (overhead) are required.

If interrupt nesting is desired, it is accomplished by first setting the MSR[EE] again as soon as it is "safe" to do so at the beginning of the interrupt service routine. Later the same EE bit must be cleared before the final context switch at the end of the interrupt service routine. In addition, the SIMASK register must be saved, lower priority interrupts masked in it, and SIMASK restored later. A conceptual example is provided in Section 7.3.6 Example 6: ISR with Nested Interrupts.

### **4** Initialization Steps

Each interrupt source must be initialized before all interrupts can be enabled in the machine state register, EE bit. Initialization consists of four steps: module specific initialization, level assignment, enabling the interrupt source, and setting the interrupt mask in the SIU interrupt controller.

The initialization steps below are broken out for illustrating completeness, and do not illustrate the most efficient programming methods.

#### 4.1 Step 1: Module Specific Initialization

Each interrupt source will need to have its own general initialization of its module. Complete module initialization is outside the scope of this application note. Examples of some module specific initializations are:

- Interrupt Pins: specify edge or level detection

- Timers: specify clock input selection, clock prescaler value, pre-loading value

- Serial I/O: specify baud rate, queue management parameters

- QADC: specify queue management parameters

- TPU, MIOS: specify function assignment, function specific parameters

#### 4.2 Step 2: Level Assignment

The system designer must make careful assignment of levels to each interrupt source. Key points to remember as discussed in the Section 3.2 USIU Interrupt Controller and Section 3.5 UIMB Module sections are summarized here:

- · Lower level numbers have higher priority

- External interrupt pins do not have level assignments but have a fixed priority

- To reduce latency, each interrupt source should be mapped to its own level if possible

- When UIMB peripherals have levels over 7, the UMCR[IRQMUX] field must be set to enable appropriate multiplexing.

The registers used for level assignments for each interrupt source are listed in **Section Appendix A Table of Potential Interrupt Sources**. Remember, level registers use either a single 5-bit field or 3-bit and 2-bit fields to assign levels as discussed in the section **Section 3.6 Interrupt Sources: UIMB Peripherals**.

#### 4.3 Step 3: Enable Interrupt

Each interrupt source other than IRQ pins must be enabled. The enable control bit for the sources are listed in **Section Appendix A Table of Potential Interrupt Sources**.

#### 4.4 Step 4: Set Appropriate Mask Bits in SIMASK

All appropriate USIU interrupt controller levels 0:8 must have their mask bits set (enabled) in the SI-MASK register.

#### 4.5 Final Step: Setting MSR[EE] and MSR[RI] Bits

After all the interrupt sources have been initialized to the previous steps, the enable external interrupts [EE] bit must be set for interrupts to be recognized and recoverable interrupt [RI] set to tell exceptions the state is recoverable. This is easily done by using the EIE special purpose register as mentioned in the prior **Section 3.1 PowerPC Core Interrupt** section. Writing any value to the EIE register sets both the MSR[EE] and MSR[RI] bits. Writing is accomplished by using the mstpr instruction.

Example: mtspr EIE, r0

### 5 Determining Which Registers to Save and Where to Save Them

Before writing software for the interrupt service routine (ISR), you must determine how much "context" to save and where to save it. In general, any registers that could be modified during in the ISR should be saved on the stack.

How much is saved can vary dramatically among applications. For example, if all software executed during the interrupt exception is written in assembler, then only those few registers used can be easily identified and saved on the stack.

However, if the ISR calls a C routine, then the compiler could use the scratch registers (called volatile registers) as defined in the EABI. Therefore, all volatile registers must be saved because it cannot be predict which registers the compiler will use. Other registers that a compiler might use will need to be saved also, such as XER (which has the carry), CR (for compares) and CTR (for counter/branch uses).

Some applications may want to even save timer values.

Table 14 is an example checklist to help determine what to save.

| ISR Requirement                                                                        | Register(s) to be Saved                                                                                                               |

|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Comply with stack conventions [EABI] used by compiler and debug tools (recommended)    | SP                                                                                                                                    |

| Additional exceptions, including debug breakpoints), are allowed during the exception. | SRR0:1                                                                                                                                |

| Use LR, (e.g., for calling an assembler or C routine handler) for an interrupt source  | LR                                                                                                                                    |

| Call assembler routines only (no floating point in ISR)                                | gprs used in routines                                                                                                                 |

| Call C routine (no floating point in ISR)                                              | Per EABI, save all volatile gprs (gpr0,<br>gpr3:12) plus any other registers that<br>a C routine could change (e.g., XER,<br>CR, CTR) |

| Complete context switch, such as with an RTOS (no floating point)                      | All gprs (gpr0:31) plus any other<br>registers that a C routine could<br>change (e.g., XER, CR, CTR)                                  |

| Use floating point registers in assembly routines only                                 | fprs used in routine                                                                                                                  |

| Use floating point in C routine                                                        | All volatile fprs (fpr0:13)                                                                                                           |

| Use floating point with complete context switch, as with an RTOS                       | All fprs (fprs 0:31)                                                                                                                  |

#### Table 14 Register Save Checklist

Registers should be saved in a stack frame, as defined in the **Section 2.7 EABI Standard**. Stack frames are created by decrementing the stack pointer by a size that can be used to store all the registers. Stack frames must be modulo eight bytes, so four bytes of padding may be required.

**Table 15** lists the EABI stack frame organization and a sample ISR stack frame. In this example, the volatile registers are saved.

|       | EABI Stack Frame | Example ISR Stack Frame                                                             |

|-------|------------------|-------------------------------------------------------------------------------------|

|       | Prior back chain | Prior SP                                                                            |

| New   | fpr save area    |                                                                                     |

| Stack | gpr save area    | Volatile gprs (gpr0, gpr3:12)                                                       |

| Frame | CR save area     | CR                                                                                  |

|       | Local variables  | CR, XER, LR, padding (if padding is re-<br>quired so stack frame is modulo 8 bytes) |

|       | LR save area     | (Reserved for function called by ISR)                                               |

|       | Back chain       | SP                                                                                  |

#### **Table 15 EABI Stack Frame Organization**

#### CAUTION

Special care should be used in saving the LR. For normal application functions, the LR is stored in the current stack frame and a new stack frame is created. However, since an exception routine function can occur anytime, the normal LR save area may already be in use. One solution is for exception routines to save the LR elsewhere on the stack, such as in the local variables area.

### 6 Interrupt Service Routine Steps

A general interrupt sequence of events is summarized in **Table 16**. When software saves special-purpose registers, a gpr must be saved also because it must be used as a scratch register for transfer purposes. These are illustrated in **Section 7.3.2 Example 2: ISR Using Assembly Language Only** through **Section 7.3.6 Example 6: ISR with Nested Interrupts**.

| System Behavior                                                                                                                              | Software Steps                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Exception occurs                                                                                                                             |                                                                                                                           |

| Currently executing instructions are completed                                                                                               |                                                                                                                           |

| The CPU saves the address of next<br>instruction and MSR[16:31] in<br>SRR0:1, then modifies MSR<br>(see <b>3.1 PowerPC Core Interrupt</b> ). |                                                                                                                           |

| The instruction pointer branches to the exception vector address.                                                                            |                                                                                                                           |

|                                                                                                                                              | 1. Save "Machine Context" of SRR0:1.                                                                                      |

|                                                                                                                                              | 2. Set MSR[RI] to indicate the state is now recoverable.<br>Other maskable interrupts/exceptions could now be<br>enabled. |

|                                                                                                                                              | 3. Save other appropriate context (registers).                                                                            |

|                                                                                                                                              | 4. Determine interrupt source.                                                                                            |

|                                                                                                                                              | 5. Branch to interrupt handler and execute it. If necessary, negate the interrupt request in the handler.                 |

|                                                                                                                                              | 6. Restore contexts, disabling maskable exceptions & clearing MSR[RI] appropriately.                                      |

|                                                                                                                                              | 7. Return to program by executing "rfi" instruction.                                                                      |

| The CPU restores return address, original MSR, and enables interrupts again.                                                                 |                                                                                                                           |

| Program execution resumes in the routine that was interrupted.                                                                               |                                                                                                                           |

#### **Table 16 Interrupt Event Sequence**

#### 6.1 Step 1: Save "Machine Context"

"Machine context" here means the save and restore registers, SRR0 and SRR1. These get loaded with the machine state by the CPU when any exception (including debugger) is taken. Therefore if another exception occurs without saving SRR0:1, the original machine state is lost. The expected normal practice is to save these on the stack. This step is not required if no other exceptions will occur during the exception routine.

Since the PowerPC architecture does not allow direct writing of special-purpose registers directly to memory, a general-purpose register must be used as an intermediary for storing these values. This means the gpr used itself must also be saved on the stack.

The PowerPC architecture does not support any hardware stack, so software will manage it. By convention (EABI), general-purpose register 1 (gpr1, or just "r1") is used for a stack pointer.

The following illustrates saving the machine context for a stack frame of size 80 bytes. Register r3 is saved so it can be used as a scratch register. We will assume the assembler has the symbol "sp" defined as "r1" for legibility. This illustration assumes what to save and where to save it on the stack frame has been defined. Complete examples are provided **Section 7 Examples of Initialization and Interrupt Service Routines**.

stwu sp, -80 (sp); Create stack frame and store back chain stw r3, 36 (sp); Save a working register in stack frame for use as a scratch register mfsrr0 r3 ; Copy SRR0 to r3 stw r3, 12 (sp); Save SRR0 value on stack mfsrr1 r3 ; Copy SRR1 to r3 stw r3, 16 (sp); Save SRR1 value on stack

#### 6.2 Step 2: Set MSR[RI]

As described earlier, the recoverable interrupt bit in the machine state register indicates the machine state can be recovered if a subsequent exception occurs. If SRR0 and SRR1 have been saved as in step 1, software should set this bit to indicate to any other exception routine this backed up condition, (i.e., recoverable state). This bit is most easily set writing any gpr to the special purpose register EID. Example:

mtspr EID, r3; Set MSR[RI] to indicate recoverable condition

Any asynchronous exception (such as reset) could check the RI bit of the MSR now saved in the SRR1. If the RI bit is 0, then the software will know the exception is non-recoverable. This can only happen if there is a reset or some major problem with either the software or the whole system.

**Debugging Comments**: Since debugging is also done by exception, if a breakpoint is taken while RI = 0, then machine state is presumed lost. In general, breakpoints are recognized in the CPU only when the RI bit is set, which guarantees that the machine restarts after a breakpoint.<sup>2</sup> In this mode, breakpoints are considered "masked". Internal breakpoints also have a non-masked mode where they are recognized at any time. If one occurs while RI=0, then the user can debug the exception routine, however at the end of the exception there is no way to return to the main program.

#### 6.3 Step 3: Save Other Appropriate Context (Registers)

Based on what else the user has determined to be saved on the stack, code will save appropriate registers. Any gpr registers can be saved with one instruction. For example:

stw r4, 40 (sp) ; Store gpr4 on stack

Special-purpose registers take two instructions, like SRR0 and SRR1. Example:

mfxer r3 ; Copy special purpose register XER to gpr3 stw r3, 20 (sp) ; Save XER value to stack

To optimize saving and later restoring context, the load / store multiple word (Imw / stmw) or load / store string word immediate (Iswi / stswi) instructions can be used. Using the multiple word or string word immediate instructions also shorten execution time. (The Imw / stmw instructions start saving registers at r31, so this would be if all the gprs would be saved.)

If interrupt nesting is to be allowed, then the SIMASK register may also need to be saved and MSR[EE] bit set. An example later illustrates how this is done.

#### 6.4 Step 4: Determine Interrupt Source

To determine the interrupt source, the following sequence can be taken:

<sup>2.</sup> MPC555 Users Manual, (MPC555UM/AD), 21.3 Watchpoints and Breakpoints Support, Rev. 1 June 2000

- Check the INTERRUPT CODE field in the USIU interrupt controller's SIVEC register, see Table

8. This value will be an index to a jump table.

- 2. If the interrupt source is level 7 and the application has interrupt sources mapped to level 7 and beyond, then check the UIPEND register for levels beyond level 7. The CNTLZW instruction can be used to count the number of zeros in the UIPEND from bit 0 until the first "1". The number can then be used as an index to a second jump table.

- 3. If more than one interrupt source shares the same level, then check both sources.

- 4. If necessary, check for which of several possible conditions within a module caused the interrupt. For example, which of 16 TPU channels caused the TPU interrupt.

The SIVEC[INTERRUPT CODE] can efficiently be used as an index into a jump table. A jump table will contain pointers to the various interrupt handlers for each source. By adding the index to the address of the start of the table, the address of the source's handler routine can be loaded into a register that can be used for branching, like the LR.

#### 6.5 Step 5: Branch to Interrupt Handler and Execute It

"Interrupt handler" here is defined as interrupt service routine code specific to a module.

Once the address of the interrupt source's handler routine is loaded in a register, then we can branch to it. The architecture allows branching from the CTR or LR registers, so the address must be loaded into one of them.

#### **IMPORTANT**

Save the address of the next instruction to the LR by using the "I" option in the branch instruction. For example:

blrl

; Jump to interrupt handler routine and save the next instructions address in LR

#### IMPORTANT

Depending on the interrupt source, it may be necessary to negate the interrupt condition so it will not cause further interrupts.

If the interrupt handler routine is written in C, the program will return to the next instruction after the above "blrl" at the end of the routine. If the routine is written in assembler, then the last instruction needs to be:

blr ; Return from interrupt handler routine to restore contexts.

#### 6.6 Step 6: Restore Contexts

Restoring contexts includes anything saved on the stack in steps 1 and 3, such as SRR0:1, gprs, etc. These are combined in one step here. Sample lines to restore some registers are:

| lwz   | r4, 40 (sp) | ; Restore gpr4 from stack        |

|-------|-------------|----------------------------------|

| lwz   | r3, 20 (sp) | ; Restore XER value from stack   |

| mtxer | r3          | ; Copy XER value to XER register |

Care must be taken to clear the MSR[RI] bit before restoring SRR0:1 to indicate an exception during restoring these registers can result in an unrecoverable condition.

As mentioned before, the load multiple word (Imw) or load string word immediate (Iswi) instructions can shorten restoring contexts.

#### 6.7 Step 7: Return to Program

A single instruction, return from interrupt, will exit the interrupt exception routine. This instruction restores the MSR from SRR1, which can re-enable exceptions such as external interrupts, the (MSR[EE] bit), floating-point unit (MSR[FP] bit) and others in the MSR. The instruction pointer gets loaded with the address in SRR0 and processing branches to that location. Example:

rfi

## 7 Examples of Initialization and Interrupt Service Routines

The following examples illustrate different techniques of handling interrupt exceptions. They have been tested on a MPC555 evaluation board with a debugger. Code was compiled using the Diab Compiler Version 4.3G. Examples 2 through 5 were tested using a standard personal computer terminal program with settings of 9600 baud, 8 data bits, no parity, 2 stop bits and no flow control. If running these programs, a standard serial cable is required, and possibly a null modem adapter.

**Initialization comments:** Interrupt initialization, such is in the "initPIT" function in the first example or "initSci" function in other examples, is written for illustration, not to optimize code.

Processor initialization, done in the function "init555", is minimal for these examples. Common items to initialize are:

- 1. SYPCR: disable watchdog timer

- 2. SIUMCR: disable data show cycles

- 3. PLPRCR: increase clock frequency using MF bit field and optionally wait for PLL to lock

- 4. UMCR: set UIMB bus to full speed using HSPEED bit

- 5. SPR560 (BBCMCR): enable burst buffer

- 6. SPR158 (ICTRL): Increase processing speed by taking processor out of serialized mode

#### 7.1 Example Interrupt Service Routines (ISRs):

- 1. Absolute minimum interrupt routine PIT

- 2. ISR using assembly language only

- 3. ISR using assembly and C

- 4. ISR using C only one interrupt source

- 5. ISR using C only general case

- 6. ISR with nested interrupt capability (conceptual example)

#### 7.2 Files Used for Examples

The files in Table 17 are used in the examples, except where noted.

#### **Table 17 Example Files**

| File Name    | Description                                                                                                                    |

|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| main.c       | Varies for each example, but always initializes the CPU and interrupt device and waits in a loop                               |

| exceptions.s | Interrupt Service Routine which calls an interrupt handler written in C or assembler. File is not used in C only examples      |

| makefile     | Common for all examples other than changing the EXECUTABLE name and sometimes removing exception.s file from the objects list. |

| link file    | Common for all examples                                                                                                        |

#### 7.2.1 Example: makefile

```

# Sample makefile for MPC555 code

# Used with DiabData compiler version 4.3g

OBJS

= main.o exceptions.o

CC

= dcc

AS

= das

= dcc

T'D

DUMP

= ddump

COPTS = -tPPC555EH:cross -@E+err.log -g -c -0 -Id:\mydoc555\m555r224

AOPTS = -tPPC555EH:cross -@E+err.log -g

LOPTS = -tPPC555EH:cross -@E+err.log -Ws -m2 -lm -l:crt0.o

EXECUTABLE = PIT

.SUFFIXES: .c .s

default: $(EXECUTABLE).elf $(EXECUTABLE).s19

.c.o :

$(CC) $(COPTS) -0 $*.0 $<

.s.o :

$(AS) $(AOPTS) $<

$(EXECUTABLE).elf: makefile $(OBJS)

$(LD) $(LOPTS) $(OBJS) -o $(EXECUTABLE).elf -Wm etas_evb.lin > $(EXECUTABLE).map

$(DUMP) -tv $(EXECUTABLE).elf >>$(EXECUTABLE).map

# Generate s record file for flashing

$(EXECUTABLE).s19: $(EXECUTABLE).elf

$(DUMP) -Rv -o $(EXECUTABLE).s19 $(EXECUTABLE).elf

```

For More Information On This Product, Go to: www.freescale.com

**MPC555 Interrupts**

```

7.2.2 Example: link file

/* etas_evb.lin file for MPC555 */

/* Memory locations 0 - 0x2000 are reserved for exception table. */

MEMORY

internal_flash:org = 0x2000, len = 0x5dff0

internal_ram:org = 0x3f9800,

len = 0x67F0

}

SECTIONS

{

GROUP : {

.text (TEXT) : {

*(.text)

*(.rodata)

*(.init)

*(.fini)

*(.eini)

. = (.+15) & ~15;

}

.sdata2 (TEXT) : { }

} > internal_flash

GROUP : {

.data (DATA) LOAD(ADDR(.sdata2)+SIZEOF(.sdata2)) : {}

.sdata (DATA)LOAD(ADDR(.sdata2)+SIZEOF(.sdata2)+SIZEOF(.data)) : {}

.sbss (BSS) : { }

.bss (BSS) : { }

} > internal_ram

}

__SP_INIT

= ADDR(internal_ram)+SIZEOF(internal_ram);

__SP_END

= ADDR(internal_ram);

____DATA_ROM

= ADDR(.sdata2)+SIZEOF(.sdata2);

_____DATA_RAM

= ADDR(.data);

____DATA_END

= ADDR(.sdata)+SIZEOF(.sdata);

___BSS_START

= ADDR(.sbss);

__BSS_END

= ADDR(.bss)+SIZEOF(.bss);

___HEAP_START

= ADDR(.bss)+SIZEOF(.bss);

___HEAP_END

= ADDR(internal_ram)+SIZEOF(internal_ram);

```

#### 7.3 Example

#### 7.3.1 Example 1: Absolute Minimum Interrupt Routine - PIT

**Summary:** This minimal example shows how to initialize and service the periodic interrupt timer (PIT) in the USIU.

**Operation:** Each PIT interrupt increments a counter variable and reloads the PIT counter. If running this program, the variables "counter" and "loopctr" can be put in a watch window of the debugger. The "counter" will show number of PIT interrupts.

There are two limitations in this example:

- 1. SIVEC[InterruptCode] is not used to determine interrupt source. Instead, the status bit is polled to determine the interrupt source. This technique would not be appropriate for more than a few interrupts.

- SRR0:1 are not saved and the MSR[RI] bit not changed, therefore the service routine is not recoverable. At least for initial coding, it is recommended to make it as done in subsequent examples.

**Stack Frame:** This interrupt service routine will not use C functions, hence few registers have to be saved. Only registers used in this assembly language routine will be saved. The stack frame layout used in the service routine is shown in **Table 18**.

| Offset from SP | Register Saved                                       |

|----------------|------------------------------------------------------|

| 20             | Unused (padding for 8-byte alignment of stack frame) |

| 16             | R5                                                   |

| 12             | R4                                                   |

| 8              | R3                                                   |

| 4              | Condition codes                                      |

| 0              | Back chain (old SP)                                  |

#### Table 18 Stack Frame Layout

#### 7.3.1.1 Example 1: Initialization and Main Routines

```

#include "mpc555.h"

// Global for ISR to hold the

UINT32 counter = 0;

// number of PIT interrupts

UINT32 loopctr = 0 ;

// Loop counter for main loop

// Simple MPC555 Initialization

void init555()

USIU.SYPCR.R = 0xfffff03;

// Disable watchdog timer

USIU.PLPRCR.B.MF = 0x009;

// Run at 40MHz for 4MHz crystal

// Wait for PLL to lock

while(USIU.PLPRCR.B.SPLS == 0);

UIMB.UMCR.B.HSPEED = 0;

// Run IMB at full clock speed

}

void initPIT()

{

// STEP 1: MODULE SPECIFIC INITIALIZATION

USIU.PITC.B.PITC = 1000;

// Setup count value.

USIU.PISCR.B.PITF = 1;

// Freeze enabled to stop PIT

USIU.PISCR.B.PTE = 1;

// PIT enabled to start counting

// STEP 2: LEVEL ASSIGNMENT

USIU.PISCR.B.PIRQ = 0x80;

// Level 0 PIT interrupt

// STEP 3: ENABLE INTERRUPT

USIU.PISCR.B.PIE = 1 ;

// Enable PIT interrupt

// STEP 4: SET APPROPRIATE SIMASK BITS

USIU.SIMASK.R = 0x40000000;

// Enable level 0; others disabled

}

main()

{

init555();

// Perform a simple 555 initialization

initPIT();

// Init PIT to generate interrupts

asm(" mtspr EIE, r3");

// FINAL STEP: SET MSR[EE], MSR[RI] BITS

while(1)

// Wait for PIT interrupts

{

loopctr++;

// Increment loopctr for something to do

}

}

```

**Freescale Semiconductor, Inc.**

#### 7.3.1.2 Example 1: Exception Service Routine for Interrupt